|

V předcházejícím příspěvku jsem ukázal řešení 6-místných digitálních hodin s multiplexovaným výstupem v jazyce VHDL. Od nich je odvozeno řešení 8-místného univerzálního čítače s multiplexovaným výstupem, který popíši v tomto příspěvku.

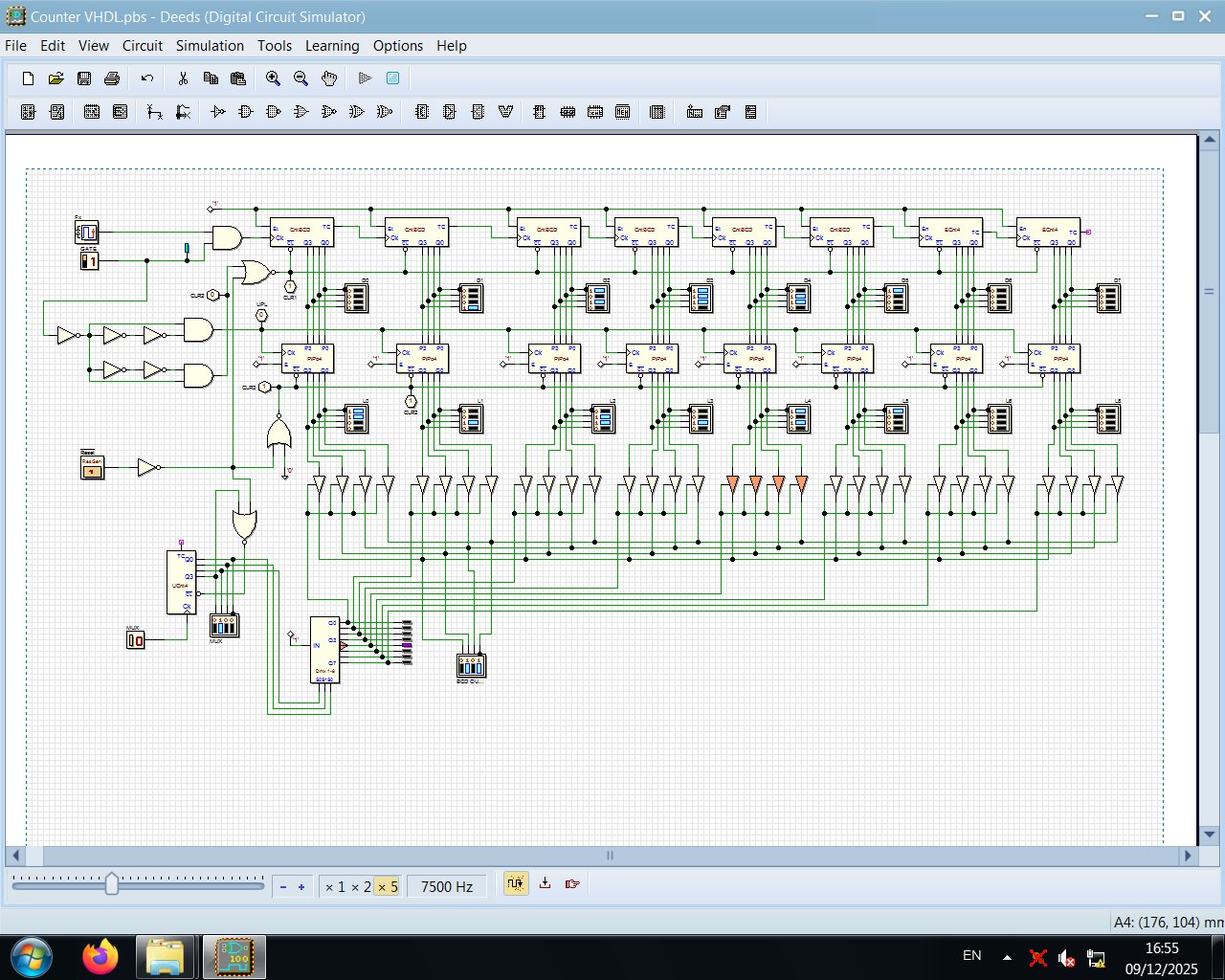

Řešení je opět provedno v programu DEEDS. Z obvodu hodin byla odstraněna hradla, která zkracovala cyklus na 60, resp. 12 a 24. Následně byly přidány dvě čítací dekády a tím rozšířen čítač na 8 míst. Zatímco hodiny ukazují permanentně stav čítačů a nemají hradlování, v případě čítače, měřiče kmitočtu nebo periody se provádí hradlování. To znamená, že se počítá počet impulzů za nějakou dobu, danou otevřením hradla. Protože hodiny přičítají neustále sekundové impulzy a nulují se po dosažení 23:59:59, čítač se nuluje vždy po uzavření hradla. Aby naměřený počet impulzů nebyl ztracen, musí se data uložit do vyrovnávací paměti. Po vynulování čítače běží další měřící cyklus a během něj displej ukazuje stav vyrovnávací paměti z předcházejícího cyklu. Do čítače je tedy nutno zařadit vyrovnávací paměti a sice ke každé dekádě samostatnou 4-bitovou paměť. Následující obrázek ukazuje schema zapojení čítače v simulátoru.

Shora dolů, první řada je 8 synchronních 4-bitových čítačů. Na jejich výstupech jsou 4-bitové LED bloky z důvodu ověření funkce. Pod řadou čítačů je osm 4-bitových vyrovnávacích pamětí. Na jejich výstupech jsou opět, z důvodu testování 4-bitové LED bloky a pod nimi se již nacházejí 4-bitové 3-stavové budiče sběrnice, které multiplexují data z vyrovnávacích pamětí na výstup.

Obr. 2 - 8-místný čítač s multiplexovaným výstupem (obrázek lze zvětšit)

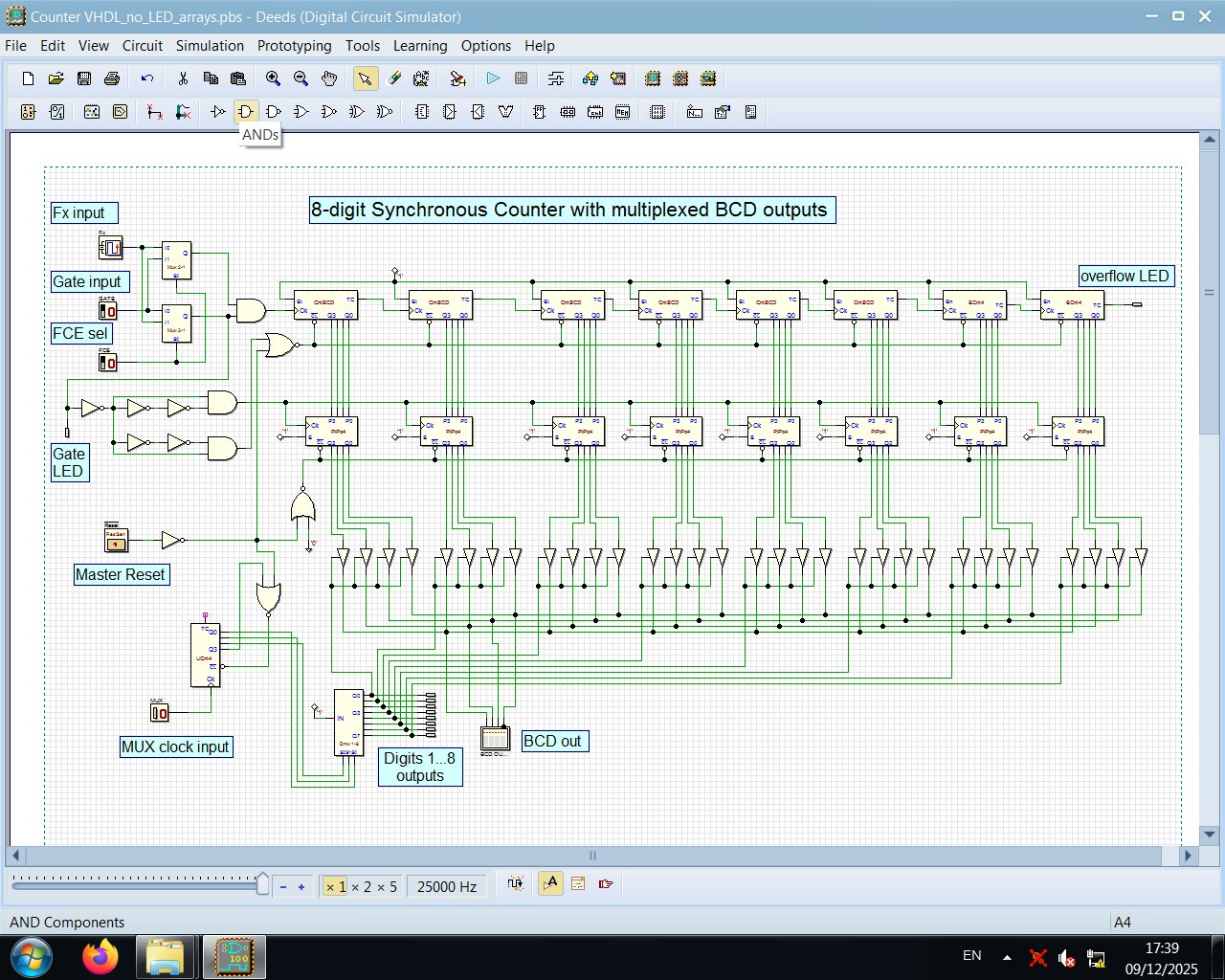

Obvod multiplexování (na schematu vlevo dole) byl rozšířen z 6 míst na 8 míst. Obvod pro multiplexování má vstup s frekvencí cca 1 kHz. Frekvenci lze snížit, ale při testování byl k dispozici právě tento signál. Na rozdíl od hodin, má čítač dva vstupy. Jednak vstup neznámé frekvence, která se má zjistit a dále hradlovací vstup, označovaný "Gate". Signál na tomto vstupu je odvozen od přesného oscilátoru. Obvody čítače musí dále zajistit, aby při konci hradlovacího signálu došlo k ulož́ení stavu čítačů do vyrovnávacích pamětí a následně byla čítací dekáda vynulována a spustil se nový měřící cyklus. Tyto funkce se provádějí pomocí hradel. Následující obrázek ukazuje celé zapojení čítače po simulaci a po odstranění 4-místných LED bloků:

Obr. 3 - 8-místný čítač s multiplexovaným výstupem (obrázek lze zvětšit)

Oproti předcházejícímu schematu byl do obvodu přidán na vstup ještě přepínač, kterým lze prohodit signál neznámé frekvence s hradlovacím signálem. Prohození těchto signálů umožní měřit periodu. To má význam především u signálů s nízkou frekvencí. K hradlování se použije právě signál s nízkou frekvencí a měří se počet impulzů ze základního oscilátoru s vysokou frekvencí.

Ve shora uvedeném řešení jsem po simulaci celého zapojení vygeneroval VHDL kód. Můžete si o něj napsat, stejně jako o grafický soubor schematu pro DEEDS. Po otestování a syntéze byl naprogramován CPLD obvod do pouzdra PLCC44. Shora uvedené zapojení lze samozřejmě realizovat klasickými TTL obvody. Nevýhodou bude, ve srovnání s CPLD obvodem, velký a nákladný plošný spoj. Test CPLD obvodu jsem provedl ve spojení s vývojovou deskou MELABS a s časovou základnou pro měřící přístroje. Tamtéž najdete schema propojení všech bloků, které tak tvoří ucelený měřící přístroj. Pro kompletní měřící přístroj je totiž k CPLD obvodu potřeba ještě časová základna a nastavovací prvky (přepínač, mikropočítač), které umožní volit co a jak se má měřit.

|