V předcházejícím příspěvku jsem ukázal základní řešení 4-místných digitálních hodin v jazyce VHDL. V tomto příspěvku popíši jejich rozšíření na 6-místné hodiny s multiplexovaným výstupem.

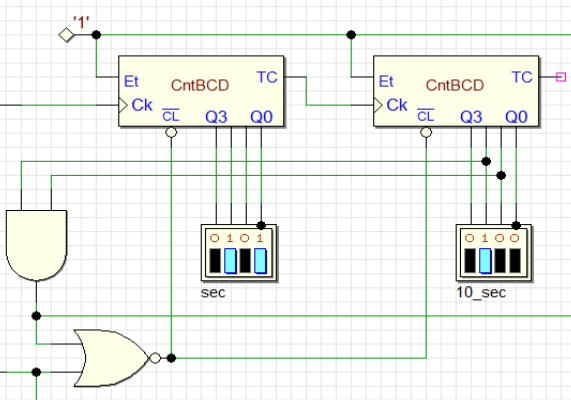

Řešení je opět provedno v programu DEEDS. Nejprve jsem přidal další 60-kový čítač pro sekundy:

Obr. 1 - 60-kový čítač sekund

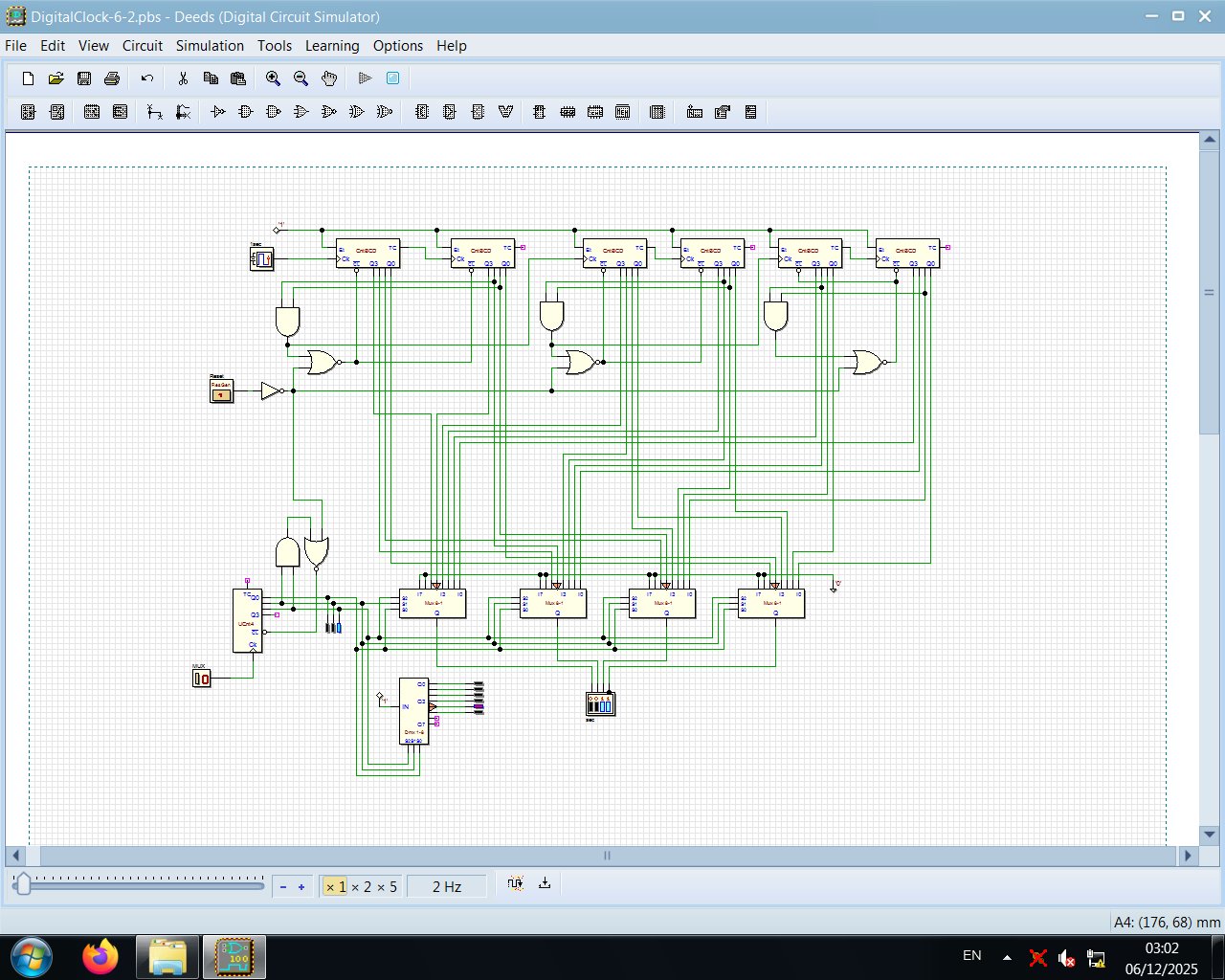

Tím se zvýšil počet BCD výstupů na 6x 4 pro každou dekádu. S ohledem na počet výstupních pinů CPLD obvodů je zřejmé, že je nutné výstup multiplexovat. Princip multiplexu jsem vysvětlil v příspěvku multiplexování LED displejů. Nyní do 6-místných hodin jsem zařadil 4 multiplexery:

Obr. 2 - 6-místné hodiny s multiplexovaným výstupem

Každý multiplexer má 8 vstupů na 1 výstup, dále 3 binární vstupy S0, S1 a S2, které nastavují jeden z osmi vstupů k výstupu. Z každého multiplexeru použijeme pouze 6 vstupů. Na první multiplexer jsou přivedeny výstupy Q0 každého čítače. Na druhý multiplexer jsou přivedeny výstupy Q1 z každého čítače. Na třetí multiplexer výstupy Q2 z každého čítače a na poslední multiplexer výstupy Q4. Multiplexery budou řízeny synchronně. Všechny multiplexery současně budou vždy připojovat přiváděné signály Q0, Q1, Q2 a Q3 z čítačů na své výstupy. Současně s tím bude volena jedna ze šesti číslovek displeje. Když multiplexery připojí na výstupy signály z prvního čítače, musí být zvolena první číslovka a tak stejně pro ostatní čítače a číslovky. O to se postará 6-kový čítač (ve schematu vlevo dole). Čítač má výstupy Q0, Q1, Q2 a pomocí hradla AND má zkrácený cyklus do 6. Jeho výstupy jsou přivedeny na binární vstupy S0, S1 a S2 každého multiplexeru. Vstupní signál do čítače pro řízení multiplexerů je 200 Hz.

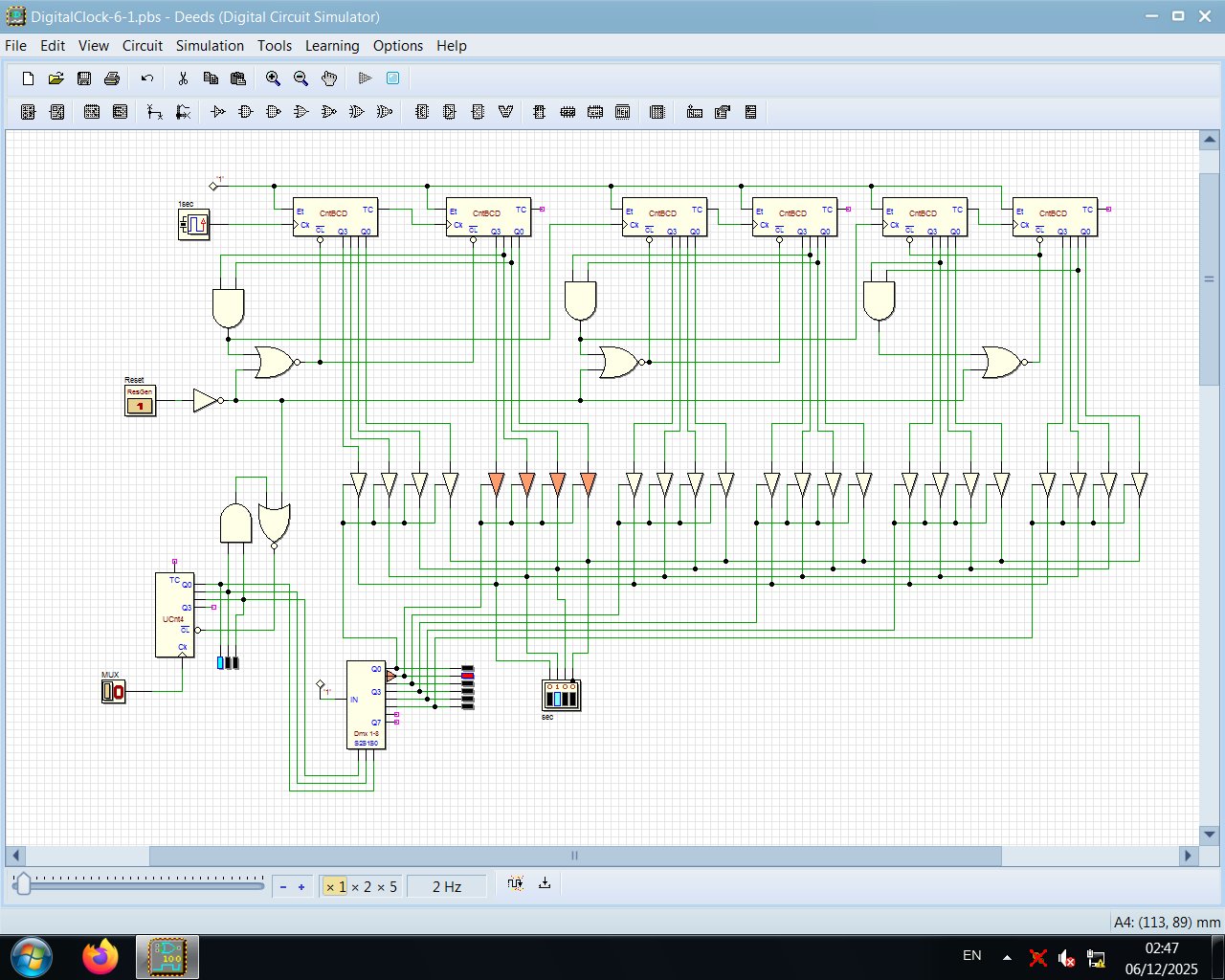

Multiplexování lze vyřešit nejen pomocí multiplexerů, ale také pomocí třístavových 4-bitových bufferů. Řešení ukazuje následující obrázek:

Obr. 3 - multiplexování pomocí třístavových bufferů

Výstupy z každého čítače jsou přivedeny na 4-bitový buffer s třístavovým výstupem. Výstupy Q0x, Q1x, Q2x a Q3x všech bufferů jsou navzájem spojeny a tvoří multiplexovaný BCD výstup hodin. Povolovací vstupy každého bufferu jsou spojeny a připojeny na výstup dekodéru, kteří spíná katody číslovek. Tím je vyřešeno, že vždy při aktivaci číslovky jsou na dekodér BCD přivedeny BCD data správného čítače. Na výstup hodin je nutno připojit vhodný dekodér BCD kódu pro displej. V případě LED displejů to může být obvod 7447 nebo 7448. Pro LCD nebo VFD displej to může být některý obvod z řady CMOS 4000.

Poznámka pro zájemce o připojení digitronů: nepřipojujte na výstup BCD přímo obvod 74141, ale multiplexovaná BCD data demultiplexujte do vyrovnávacích 4-bitových pamětí a teprve na tyto paměti připojte dekodéry a spínače digitronů 74141. Multiplexováním digitronů se zkracuje jejich životnost.

V obou shora uvedených řešeních jsem provedl simulaci celého zapojení a vygeneroval VHDL kódy. Můžete si o ně napsat, stejně jako o grafický soubor schematu pro DEEDS. Do schematu zbývá doplnit tlačítka pro nastavování hodin (tlačítko STOP, SLOW a FAST). Dále lze doplnit vstupní děličku pro vstup signálu s vyšším kmitočtem než 1 Hz. Hodiny je možné rozšířit také o budík nebo minutku. Vytvoříte si tak vlastní integrovaný obvod pro digitální hodiny.

|