Digitální hodiny si můžete sami navrhnout snadno a velmi rychle. Práce vám zabere tak 2 nejvýše 3 hodiny. Co k tomu potřebujete:

- simulační program DEEDS.

- základní znalost logických obvodů, tedy hradel, čítačů, klopných obvodů

- konvertor VHDL -> JEDEC

- programátor JEDEC s nějakou vývojovou deskou pro hradlová pole

Simulační program DEEDS je vytvářený na univerzitě v italské Genoa již od roku 2013. Software je velmi propracovaný a je freeware. Naučit se ním pracovat zabere nejvýše jeden víkend. DEEDS funguje nad MS Windows. Já jej provozuji nad verzí 7.

Základní znalosti logických obvodů, to znamená, musíte znát co to jsou hradla AND, NAND, OR, NOR, EX-OR, klopné obvody, čítače, posuvné registry, atd atd. K tomu samozřejmě Booleovu algebru a binární aritmetiku, To vše je nezbytná výbava pro konstrukce digitálních systémů. Znalost kódování Arduina vám v tomto směru bude k ničemu.

Konvertor z jazyka VHDL do JEDEC je software. Je zahrnut například v CAE návrhovém systému EdwinXP. Existují však samostatné konverzní programy a také možnosti překladu na cloudech na internetu.

Programátor JEDEC do hradlového pole můžete koupit čínský na eBay nebo firemní s nějakou vývojovou destičkou. Já používám vývojovou desku DK3-U od Microchip. Viz příspěvek digitální minutka s CPLD obvodem. Součástí vývojové destičky je také programátor.

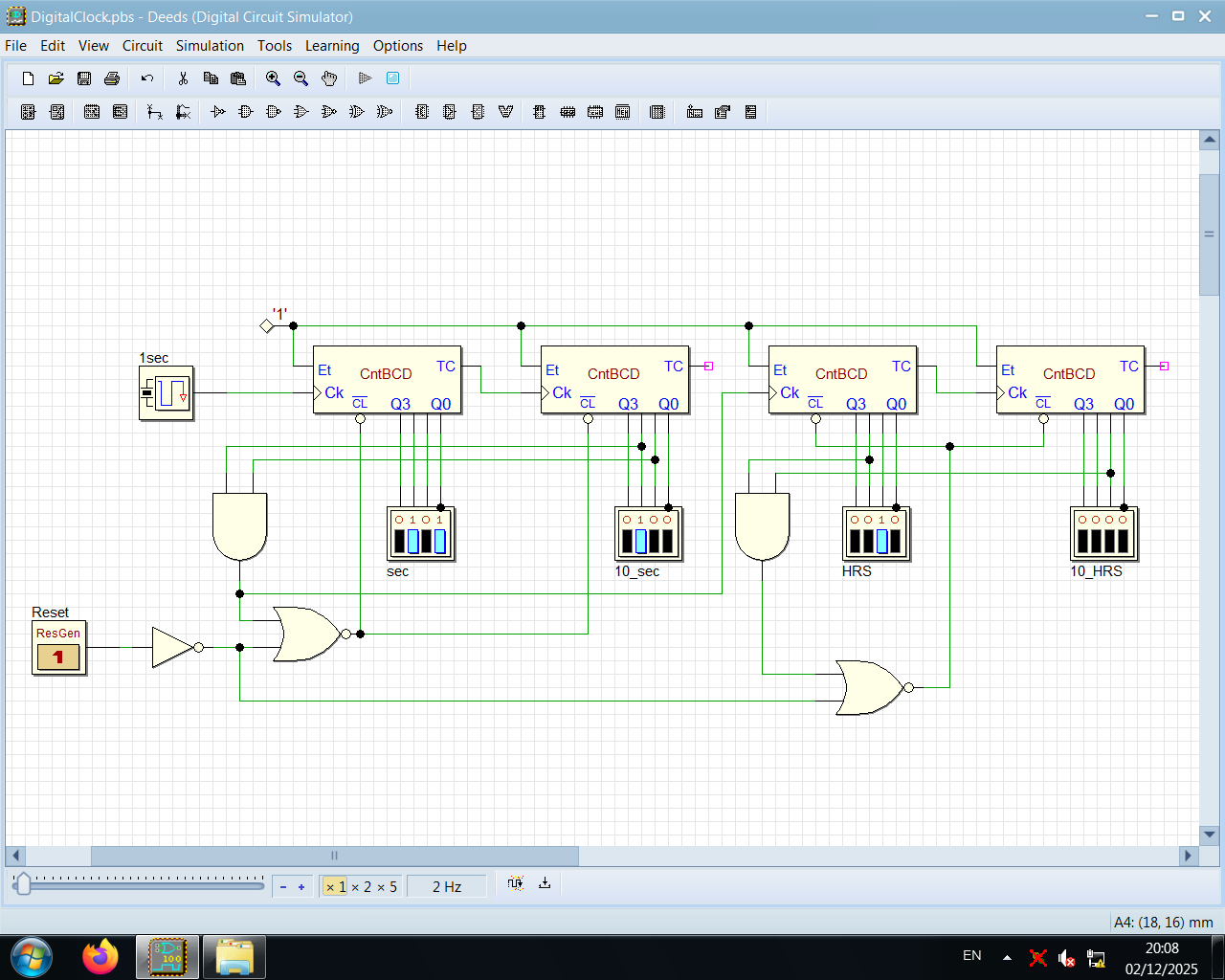

Následující obrázek je printscreen ze simulačního obvodu DEEDS s navrženými 4-místnými hodinami s rozsahem 24 hodin.

Obr. 1 - digitální hodiny v simulačním programu DEEDS (kliknutím na obrázek jej lze zvětšit)

Nakreslení schematu mi zabralo asi 20 minut. Následovalo otestování, zda zapojení správně funguje. Dalším krokem bylo vygenerování souboru ve VHDL. Program DEEDS generuje VHDL soubor během zlomku sekundy. V záhlaví výpisu je uveden odkaz na stránku univerzity, kde lze zdarma získat program DEEDS.

Vygenerovaný soubor ve VHDL:

------------------------------------------------------------

-- Deeds (Digital Electronics Education and Design Suite)

-- VHDL Code generated on (02/12/2025, 20:02:50)

-- by Deeds (Digital Circuit Simulator)(Deeds-DcS)

-- Ver. 3.02.349 (Oct 1, 2025)

-- Copyright (c) 2002-2025 University of Genoa, Italy

-- Web Site: https://www.digitalelectronicsdeeds.com

------------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.all;

ENTITY DigitalClock IS

PORT(

--------------------------------------> Inputs:

iReset: IN std_logic;

i1sec: IN std_logic;

--------------------------------------> Outputs:

o10_sec: OUT std_logic_vector( 3 downto 0 );

osec: OUT std_logic_vector( 3 downto 0 );

oHRS: OUT std_logic_vector( 3 downto 0 );

o10_HRS: OUT std_logic_vector( 3 downto 0 )

------------------------------------------------------

);

END DigitalClock;

ARCHITECTURE structural OF DigitalClock IS

----------------------------------------> Components:

COMPONENT NOT_gate IS

PORT( I: IN std_logic;

O: OUT std_logic );

END COMPONENT;

--

COMPONENT AND2_gate IS

PORT( I0,I1: IN std_logic;

O: OUT std_logic );

END COMPONENT;

--

COMPONENT NOR2_gate IS

PORT( I0,I1: IN std_logic;

O: OUT std_logic );

END COMPONENT;

--

COMPONENT CounterBCD4 IS

PORT( Ck : IN std_logic;

nCL: IN std_logic;

ENT: IN std_logic;

Q3 : OUT std_logic;

Q2 : OUT std_logic;

Q1 : OUT std_logic;

Q0 : OUT std_logic;

Tc : OUT std_logic );

END COMPONENT;

----------------------------------------> Signals:

SIGNAL S001: std_logic;

SIGNAL S002: std_logic;

SIGNAL S003: std_logic;

SIGNAL S004: std_logic;

SIGNAL S005: std_logic;

SIGNAL S006: std_logic;

SIGNAL S007: std_logic;

SIGNAL S008: std_logic;

SIGNAL S009: std_logic;

SIGNAL S010: std_logic;

SIGNAL S011: std_logic;

SIGNAL S012: std_logic;

SIGNAL S013: std_logic;

SIGNAL S014: std_logic;

SIGNAL S015: std_logic;

SIGNAL S016: std_logic;

SIGNAL S017: std_logic;

SIGNAL S018: std_logic;

SIGNAL S019: std_logic;

SIGNAL S020: std_logic;

SIGNAL S021: std_logic;

SIGNAL S022: std_logic;

SIGNAL S023: std_logic;

SIGNAL S024: std_logic;

SIGNAL S025: std_logic;

SIGNAL S026: std_logic;

----------------------------------------> Not Connected Pins:

SIGNAL ncp8_C002: std_logic;

SIGNAL ncp8_C152: std_logic;

BEGIN -- structural

----------------------------------------> Input:

S010 <= iReset;

S026 <= i1sec;

----------------------------------------> Output:

o10_sec(0) <= S001;

o10_sec(1) <= S009;

o10_sec(2) <= S008;

o10_sec(3) <= S002;

osec(0) <= S003;

osec(1) <= S004;

osec(2) <= S005;

osec(3) <= S006;

oHRS(0) <= S013;

oHRS(1) <= S014;

oHRS(2) <= S022;

oHRS(3) <= S015;

o10_HRS(0) <= S018;

o10_HRS(1) <= S023;

o10_HRS(2) <= S017;

o10_HRS(3) <= S016;

----------------------------------------> Constants:

S019 <= '1';

----------------------------------------> Component Mapping:

C001: CounterBCD4 PORT MAP ( S026, S007, S019, S006, S005,

S004, S003, S011 );

C002: CounterBCD4 PORT MAP ( S011, S007, S019, S002, S008,

S009, S001, ncp8_C002 );

C105: AND2_gate PORT MAP ( S009, S008, S025 );

C127: NOR2_gate PORT MAP ( S025, S012, S007 );

C138: NOT_gate PORT MAP ( S010, S012 );

C151: CounterBCD4 PORT MAP ( S025, S024, S019, S015, S022,

S014, S013, S020 );

C152: CounterBCD4 PORT MAP ( S020, S024, S019, S016, S017,

S023, S018, ncp8_C152 );

C184: AND2_gate PORT MAP ( S023, S022, S021 );

C197: NOR2_gate PORT MAP ( S021, S012, S024 );

END structural;

Tento soubor je nutno nyní zkonvertovat do formátu JEDEC. To provedeme v návrhovém systému CAE edwinXP (navrhuji jím plošné spoje). Vzniklým souborem ve formátu JEDEC pak musíme naprogramovat hradlové pole. Před tím je však nutno provést ještě syntézu a simulaci na konkrétní hradlové pole. Syntéza a simulace se provádí pomocí software dodávaných s vývojovým kitem DK3-U od Microchip. Můžete samozřejmě použít také jiné vývojové desky, například od Digilent nebo Xilinx. O vývojovém kitu DK3-U od Microchip, o syntéze a simulaci se dočtete v jiném článku.

|